### computing@computingonline.net www.computingonline.net

Print ISSN 1727-6209 On-line ISSN 2312-5381 International Journal of Computing

# POWER-CONSUMPTION-ORIENTED CHECKABILITY FOR FPGA-BASED COMPONENTS OF SAFETY-RELATED SYSTEMS

Oleksandr Drozd <sup>1)</sup>, Viktor Antoniuk <sup>1)</sup>, Miroslav Drozd <sup>1)</sup>, Volodymyr Karpinskyi <sup>2)</sup>, Pavlo Bykovyy <sup>3)</sup>

Odessa National Polytechnic University, 1, Shevchenko Ave., 65044, Odessa, Ukraine drozd@ukr.net, viktor.v.antoniuk@gmail.com, miroslav\_dr@mail.ru

<sup>2)</sup> Rolls-Royce plc., Watnall Road, Hucknall, NG15 6EU, UK vkarpinskyi@gmail.com

<sup>3)</sup> Ternopil National Economic University, 3 Peremohy Square, Ternopil, Ukraine, 46020, pb@tneu.edu.ua

#### Paper history:

Received 13 March 2019 Received in revised form 4 May 2019 Accepted 19 June 2019 Available online 30 June 2019

### Keywords:

safety-related system; logical checkability; hidden fault; common signal; FPGA; power checkability. Abstract: This paper is dedicated to the problem of the circuit checkability of components in the safety-related systems, which operate objects of the increased risk and are aimed at ensuring safety of both a system and a control object for accident prevention and a decrease in their consequences. Importance of the checkability of the circuits for ensuring safety in critical applications is emphasized as safety is based on the use of fault tolerant circuitry decisions and their efficiency is defined by the circuit checkability. Development of a logical checkability from testability to structurally functional and dual-mode model which formalizes a problem of the hidden faults and defines ways of its solution is shown. The limitation of a logical checkability in detection of faults in chains of the common signals and the need for development of checkability out of the limits of a logical form, including suitability to checking the circuits on the basis of their power consumption is considered. Power-consumption-oriented checkability (Power-checkability) allowing detection of faults in chains of the common signals is defined. Its analytical assessment for the circuits implemented in FPGA is offered. Experiments providing estimation of power-checkability for FPGA-implementation of iterative array multipliers with various activities of input signals are carried out.

Copyright © Research Institute for Intelligent Computer Systems, 2019.

All rights reserved.

#### 1. INTRODUCTION

A checkability of the digital circuit is its suitability for monitoring the presence of a fault in it. The importance of this indicator increases with the expansion of the area of critical information technology applications that underlie instrumentation and control safety-related systems. These systems manage high-risk objects, including transportation infrastructures, power grids and power plants, as well as other areas relevant to people's livelihoods. Safety-related systems are focused on ensuring safety of the control object. Solving this problem requires ensuring functional safety also for the control system itself.

The amount of critical applications is increasing. Their complexity and power growth create the prerequisites for increasing the risk of accidents.

Safety, which becomes the main argument in the prevention of man-made disasters, is based on the use of fault tolerant solutions.

The main threat to their effectiveness comes from the hidden processes that can lead to the accumulation of many hidden faults. The amount of these faults may exceed the possibilities of fault-tolerant solutions for their parrying. Such circumstances appear because of insufficient checkability of the circuits in the components of safety-related systems.

Therefore, ensuring of safety requires improvement in the circuit checkability, which can be significantly reduced with the growing complexity of the circuits themselves. Fault-tolerant solutions become effective in ensuring the safety of safety-related systems only when performing a condition of the system's checkability, which begins with the checkability of its components.

### 2. RELATED WORKS, GOAL AND STRUCTURE OF THE PAPER

Requirements for safety-related systems are regulated by international standards that define safety and measures to ensure it for the system and for the control object to prevent accidents and reduce the consequences if they occur [1].

Safety-related systems can be considered as the development of computer systems with the division of the operating mode into two modes: normal and emergency, which have significant differences. The normal mode is the longest and can be considered as waiting in relation to the emergency mode. Emergency mode is the most responsible and least studied. In these modes, digital circuits can receive various input data, for example, they can operate in normal mode at the noise level and receive useful signals only when the emergency mode starts [2, 3].

The limited set of input data makes the digital circuit structurally redundant. This reduces the checkability of the circuit.

As a rule, safety is supported by fault-tolerant solutions based on configurable units, correcting codes, majority structures and multi-version technologies [4, 5]. Multi-version solutions allow to resist to common cause failures that may occur, for example, due to design errors [6].

Fault-tolerant circuit solutions significantly complicate the digital components of safety-related systems, repeatedly increasing their structural redundancy and complexity.

Generally, the checkability of a digital circuit is defined as its suitability for performing logical checking, which is considered as the possibility of detecting a fault, using for this the error of the result calculated at the output of this circuit in testing or operating mode [7, 8].

Logical checkability is best known as testability, i.e., suitability to test development for detecting faults in the process of testing of the circuit. Testability is the simplest form of logical checkability. It depends only on the structure of the

circuit, and, therefore, is called structural checkability [9].

In on-line testing [10, 11], the logical checkability of the digital circuit becomes structurally-functional, since it depends not only on the structure of the circuit, but also on the input data processed in an operating mode. The possibilities of on-line testing of the digital circuits are completely limited by its structurally-functional checkability.

Safety-related systems, as well as other cyberphysical systems, including IoT, receive input data from sensors. These data are measurement results, i.e., they refer to approximate data, which is usually processed in floating-point formats [12, 13].

Performing operations in floating-point arithmetic greatly complicates circuit design solutions both in terms of organizing main calculations and in checking them. Mantissa processing is most efficiently performed by using the truncated operations [14, 15]. These operations retain a single accuracy of computations, however, they significantly complicate checking schemes, including residue checking, which is the main method of on-line testing the arithmetic nodes [16, 17].

The complication of the circuits in the main and checking operations reduces their logical checkability.

The logical checkability gained development in the theory and practice of creation of the totally self-checking circuits [18]. Self-checking of these circuits increases structurally-functional checkability in error detection schemes when the self-testing condition is met [19].

However, in safety-related systems, structurally-functional checkability becomes dual-mode, i.e., different for a normal and emergency modes due to different input data. This difference creates a problem of the hidden faults that can be accumulated over the course of a long-term normal mode and manifest themselves in reducing the fault tolerance of the circuits in most critical emergency modes [20].

The main approach to a solution of the hidden fault problem is the use of the imitation modes which recreate emergencies and more than once brought to them as a result of unauthorized activation of the emergency mode by a person or a fault [21, 22].

The use of hazardous imitation modes aimed at improving the checkability of safety-related systems indicates a lack of confidence in the effectiveness of the fault-tolerant solutions and the lack of checkability to support this effectiveness.

We can distinguish two groups of methods of the logical checkability improvement for solving the problem of hidden faults without use of the imitation modes. The first group of methods is aimed at improving the structurally-functional checkability of circuits in normal mode to counteract the accumulation of hidden faults.

Another group of methods aligns the structurally-functional checkability of the normal and emergency modes in order to remain the hidden faults of the normal mode in the emergency mode and to detect the faults of the emergency mode during the long-term normal mode [20].

Both groups of methods are focused on the implementation of digital components on FPGA (Field Programmable Gate Array) using modern CAD (Computer-Aided Design) systems. This feature makes them attractive for safety-related systems, which receive a number of advantages when designing on FPGA [23].

However, these methods are significantly limited by the complexity of modern circuits, a number of requirements imposed by standards to safety-related systems and opportunities of the logical checkability which is in certain dependence on the faults arising in chains of the common signals, such as signals of reset and synchronization [24].

Thus, ensuring the checkability of circuits for safety-related systems is an important and urgent task that requires its solution without the use of the dangerous imitation modes. Ensuring logical checkability faces the considerable complexity of modern circuit solutions both in the building of fault-tolerant components and the limitations of the standards, governing their development for safety-related systems. These arguments stimulate the search for new solutions, including those outside the logical form of checkability.

The goal of this article is to develop a new form of checkability as the suitability of a circuit for checking based on an assessment of its power consumption which allows detecting faults in chains of the common signals. Major scientific contribution is made to solving the hidden fault problem concerning common signals on the basis of assessment and the use of checkability associated with power consumption of FPGA components in safety-related systems.

Section 3 defines power-consumption-oriented checkability (power-checkability) and gives its

analytical evaluation for the circuits designed on FPGA. Section 4 describes experiments with FPGA projects to evaluate their power-checkability and analyzes the results of these experiments.

### 3. POWER-CHECKABILITY DEFINITION

The circuit checkability can be estimated by the ratio of the  $P_F$  volume of ranges of impossible power consumption values, which uniquely characterizes the circuit as faulty, to the  $P_T$  volume of a whole range of power consumption values,  $P_T = P_F + P_C$ , where  $P_C$  is the volume of a range of possible power consumption values.

The  $R_C$  range of possible values of power consumption allocates two ranges of impossible values in the entire  $R_T$  range: upper  $R_U$  and lower  $R_L$ , for which their volumes  $P_U$  and  $P_L$  make up the volume  $P_F = P_U + P_L$ . Volumes  $P_U$  and  $P_L$ , referred to the entire volume of  $P_T$ , determine the upper and lower checkability of the circuit, respectively.

Upper checkability determines the detection of faults that significantly increase power consumption, for example, in the event of a short circuit.

Lower checkability is focused on faults that significantly reduce power consumption. This reduction of power consumption occurs in its dynamic component, which is proportional to the number of transitions switching signals in the circuit. A significant reduction in the number of transitions is caused by faults that violate common signal circuits, such as, for example, reset and synchronization signals.

Faults in common signals pose a significant threat to safety-related systems, as they can be hidden from logical checking due to its blocking in a state that indicates the absence of a fault.

Thus, logical checkability does not cover a set of faults arising in common signal circuits. For their detection, it is necessary to develop alternative forms of checkability, including power-oriented checkability. Further, we consider the lower checkability, which is important for detection of faults in chains of the common signals.

Taking into account the constant value of the supply voltage, the values of consumed power are replaced in the assessment of checkability with the values of current consumption. Lower checkability, which takes into account the influence of only the dynamic component of the power consumption, is accordingly determined using the dynamic component of the current consumption as follows:

$$C_{P.L} = I_{DMIN}/I_{DMAX}$$

where  $I_{DMIN}$  and  $I_{DMAX}$  — the minimum and maximum values of dynamic component of the current consumption, respectively.

Power-checkability  $C_{P,L}$  essentially depends on the conditions of the circuit designing. We are reviewing Quartus Prime 17.1 Lite Edition (Intel FPGA) [25], which estimates power consumption using its PowerPlay Power Analyzer utility [26].

Similar utilities, for example, XPower Analyzer, are also used in other recognized CAD systems, in this case in Xilinx ISE [27].

It should be noted that Intel FPGA (former Altera) and Xilinx are world leaders in FPGA design and produce 38% and 49% of products in this market, respectively [28].

Power monitoring of the circuit can be performed in its operating mode by measuring the current consumption. We can judge the dynamic component  $I_D$  by subtracting its static component  $I_S$  from the measured  $I_T$  current consumption, which can be estimated previously by means of the PowerPlay Power Analyzer utility.

We can assess checkability using simulation and measurement results taking into account their errors.

The minimum  $I_{D \ MIN}$  value of the dynamic current consumption component can be estimated as follows:

$$I_{D MIN} = I_T - I_S - \Delta I_T - \Delta I_S, \tag{1}$$

where  $\Delta I_T$  and  $\Delta I_S$  – an absolute value of the error of current consumption  $I_T$  and its static component  $I_S$ , respectively.

Formula (1), taking into account the equality  $I_T - I_S = I_D$ , is converted to the following form:

$$I_{DMIN} = I_D - \Delta I_T - \Delta I_S, \qquad (2)$$

The maximum  $I_{DMAX}$  value of the dynamic component of current consumption can be received similarly taking into account the increasing errors and possible increase in activity of signals at circuit inputs:

$$I_{DMAX} = I_D^* + \Delta I_T^* + \Delta I_S^*, \tag{3}$$

where  $I_D^*, \Delta I_T^*, \Delta I_S^*$  – the dynamic component of current consumption, an absolute value of the error of current consumption and its static component for a case of the increased activity of input signals.

Then the lower power-oriented checkability is

evaluated with regard to (2) and (3) by the following formula:

$$C_{PL} = (I_D - \Delta I_T - \Delta I_S) / (I_D^* + \Delta I_T^* + \Delta I_S^*).$$

(4)

The PowerPlay Power Analyzer utility estimates the current consumption of  $I_T$ , as well as its dynamic  $I_D$  and static  $I_S$  components with an error of  $\Delta = \pm 2.5\%$ . Sensors for measuring current consumption work with the same error.

Then, formula (4), taking into account  $\Delta I_T = \Delta I_S = 2.5\%$  and  $\Delta I_T^* = \Delta I_S^* = 2.5\%$ , takes the following form:

$$C_{P.L} = (I_D - 0.025 I_T - 0.025 I_S) / (1.025 I_D).$$

The parameters  $I_D$ ,  $I_S$  and  $I_T$  of power-checkability  $C_{P.L}$  can change their values under the influence of the activity of signals that are fed to the inputs of the circuit. Therefore, the power-checkability  $C_{P.L}$  should be investigated with different input signal activity. The final result is the smallest power-checkability  $C_{P.L}$ .

The assessment methodology contains the following sequence of steps:

- Designing in Quartus Prime a project of a multiplier of a given range.

- Compiling a project in Quartus Prime that results in determining the allowed synchronization frequency for the project.

- Setting up time parameters (frequency) in the utility Time Quest Timer Analyzer.

- Re-compiling the project with the established time parameters.

- Setting up in the Power Play Power Analyzer utility a given value for the activity of informational (input / output and internal) signals of the project as a percentage of the clock signal activity (frequency).

- -Running a simulation in Power Play Power Analyzer, which determines the total current consumption of the core  $I_T$  and its static  $I_S$  and dynamic  $I_D$  components.

- Calculating by formula (4) the checkability value for the given multiplier design and given informational signals activity.

## 4. EXPERIMENTAL ASSESMENT OF LOW POWER-CHECKABILITY

Power-checkability  $C_{P,L}$  is determined for iterative array multiplier circuits of binary numbers based on simulation results that were run on Intel

Max 10 10M50DAF672I7G FPGA containing 288 9-bit multiplication blocks with input and output buffer registers [29].

The multiplication blocks in Quartus Prime are designed on the basis of the LPM\_MULT multiplier from the Intellectual Property Core (IP-Core) of the Library of Parameterized modules (LPM), which is a part of Quartus Prime [30].

In the course of the experiments, FPGA projects of iterative array multipliers with the size of operands n = 16, 32, 48 and 64 were implemented. The input signals activity  $A_I$  was set using the PowerPlay Power Analyzer utility in the range from 0% to 100% in relation to the synchronization signal of the multiplier registers with increments of 12.5%.

The simulation results which are the parameters  $I_D$ ,  $I_S$  and  $I_T$  for a core of FPGA chip are shown in Tables 1-4 for n from 16 to 64 bits, respectively.

Table 1. Experiment results for n = 16

| A <sub>I</sub> , % | $I_D$ , mA | I <sub>S</sub> , mA | $I_T$ , mA |

|--------------------|------------|---------------------|------------|

| 0                  | 7.76       | 11.75               | 19.51      |

| 12.5               | 8.61       | 11.76               | 20.36      |

| 25                 | 9.46       | 11.76               | 21.22      |

| 37.5               | 10.31      | 11.76               | 22.08      |

| 50                 | 11.16      | 11.77               | 22.93      |

| 62.5               | 12.02      | 11.77               | 23.79      |

| 75                 | 12.87      | 11.78               | 24.64      |

| 87.5               | 13.72      | 11.78               | 25.50      |

| 100                | 14.57      | 11.79               | 26.36      |

Table 2. Experiment results for n = 32

| $A_I$ , % | $I_D$ , mA | $I_S$ , mA | $I_T$ , mA |

|-----------|------------|------------|------------|

| 0         | 16.28      | 11.93      | 28.21      |

| 12.5      | 19.25      | 11.94      | 31.19      |

| 25        | 22.22      | 11.95      | 34.17      |

| 37.5      | 25.20      | 11.96      | 37.16      |

| 50        | 28.17      | 11.97      | 40.14      |

| 62.5      | 31.14      | 11.99      | 43.13      |

| 75        | 34.11      | 12.00      | 46.11      |

| 87.5      | 37.08      | 12.01      | 49.09      |

| 100       | 40.06      | 12.02      | 52.08      |

Table 3. Experiment results for n = 48

| $A_I$ , % | $I_D$ , mA | $I_S$ , mA | $I_T$ , mA |

|-----------|------------|------------|------------|

| 0         | 34.07      | 12.11      | 46.18      |

| 12.5      | 39.61      | 12.13      | 51.74      |

| 25        | 45.15      | 12.15      | 57.30      |

| 37.5      | 50.69      | 12.17      | 62.87      |

| 50        | 56.23      | 12.19      | 68.43      |

| 62.5      | 61.77      | 12.22      | 73.99      |

| 75        | 67.31      | 12.24      | 79.55      |

| 87.5      | 72.85      | 12.26      | 85.11      |

| 100       | 78.39      | 12.28      | 90.67      |

Table 4. Experiment results for n = 64

| $A_I$ , % | $I_D$ , mA | Is, mA | $I_T$ , mA |

|-----------|------------|--------|------------|

| 0         | 60.23      | 12.32  | 72.55      |

| 12.5      | 70.05      | 12.35  | 82.40      |

| 25        | 79.87      | 12.39  | 92.26      |

| 37.5      | 89.69      | 12.42  | 102.11     |

| 50        | 99.51      | 12.45  | 111.97     |

| 62.5      | 109.33     | 12.49  | 121.82     |

| 75        | 119.15     | 12.52  | 131.68     |

| 87.5      | 128.97     | 12.56  | 141.53     |

| 100       | 138.79     | 12.59  | 151.39     |

Power-checkability  $C_{P,L}$  is calculated for  $I_{DMIN}$  which is estimated at zero activity of input signals, and  $I_{DMAX}$  received in case of an increase in activity  $A_I$  of input signals for value  $\Delta A_I = 12.5\%$  from 0 to 100%.

Results of power-checkability assessment represented as a percentage are shown in Table 5.

Table 5. Assessment of Power-checkability

| A <sub>I</sub> , % | n = 16 | n = 32 | n = 48 | n = 64 |

|--------------------|--------|--------|--------|--------|

| 0                  | 81.70  | 88.39  | 91.80  | 93.19  |

| 12.5               | 74.14  | 75.15  | 79.14  | 80.24  |

| 25                 | 67.85  | 65.36  | 69.56  | 70.45  |

| 37.5               | 62.55  | 57.80  | 62.04  | 62.78  |

| 50                 | 58.02  | 51.83  | 55.99  | 56.62  |

| 62.5               | 54.06  | 46.98  | 51.02  | 51.57  |

| 75                 | 50.64  | 42.96  | 46.85  | 47.34  |

| 87.5               | 47.63  | 39.57  | 43.32  | 43.75  |

| 100                | 44.95  | 36.67  | 40.28  | 40.67  |

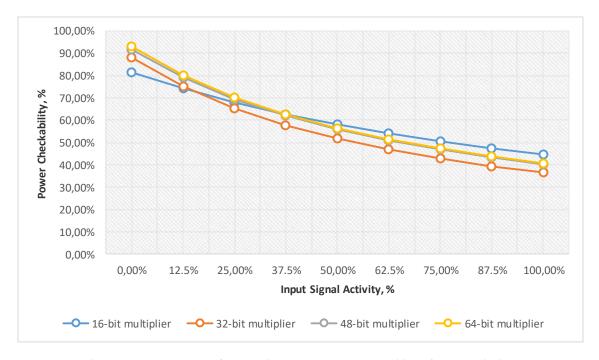

Graphics of the power-checkability dependence on change in signal activity are shown in Fig. 1.

Figure 1 – The results of evaluating the power-checkability of the multipliers when the activity of the input signals changes

The graphics show the monotonous nature of change in the checkability, which raises with decrease in possible change of activity of the input signals.

For 16-, 32-, 48-, 64-bit multipliers, the greatest power-checkability values are reached at the minimum changes in activity of the input signals: 81.70%, 88.39%, 91.80%, 93.19% and 74.14%, 75.15%, 79.14%, 80.24% in cases  $A_I = 0$  and  $A_I = 12.5\%$ , respectively.

Changes in activity of the input signals over a wide range reduce power-checkability: 58.02%, 51.83%, 55.99%, 56.62% and 54.06%, 46.98%, 51.02%, 51.57% in cases  $A_I = 50\%$  and  $A_I = 62.5\%$ , respectively.

At the same time, even in an exceptional case of  $A_I = 100\%$ , power-checkability shows values from 36.67% to 44.95% which keep the considerable range of values of a dynamic component in the current consumption for detection of faults in chains of the common signals.

It should be noted that Power-checkability, as a rule, grows with increase in operand size of multipliers. The exception makes only operand size 16 for  $\Delta A_I \ge 50\%$ .

### 5. CONCLUSION

The checkability of the circuit plays a pivotal role in providing the effectiveness of fault-tolerant solutions used in safety-related systems to ensure the safety of the system itself and the control objects.

Understanding the logical checkability of the circuits was developed from testability to

structurally-functional and dual-mode structurally-functional models, which allowed to determine the problem of the hidden faults and ways to solve it without using dangerous imitation modes.

However, the possibilities of improving logical checkability are limited by the growing complexity of modern circuit solutions.

In addition, the logical checkability and decisions developed in its framework, including methods of its improvement and on-line testing methods, are limited in detection of faults which arise in chains of the common signals playing an important role in functioning of the digital circuits. These faults can block the check circuits and the error detection results.

The development of circuit checkability by estimating its power consumption, that has been proposed, is provided by the necessary tools of evaluation in modern systems of digital component design on FPGA.

Power-checkability allows to detect faults in the circuits of common signals in reducing the dynamic component of power consumption.

Analytical assessment of power-checkability is based on the current consumption and its dynamic and static components, which reflect the power consumption at a constant supply voltage.

Experiments for power-checkability evaluations based on the dynamic component of the consumed current were performed on Quartus Prime 17.1 Lite Edition (Intel FPGA) CAD software using an intelligent LPM\_MULT module for a range of

iterative array multipliers sizes and activity levels of the input circuit signals.

The experiments that have been carried out showed a high level of power-checkability, which raises with the decrease in change of activity of the input signals and, as a rule, grows with increase in complexity of circuits.

In the most widespread cases if a change in activity of the input signals does not exceed 25% and 50%, power-checkability exceeds 50% and 65%, respectively. Thus, more than a half of range of values in a dynamic component of the current consumption lies in the area of impossible values which allow detecting faults in chains of the common signals.

Complication of iterative array multipliers while increasing the size of operands from 32 to 64 bits raises power-checkability of their circuits unlike a logical checkability which decreases with the growth of circuit complexity.

### 6. REFERENCES

- [1] IEC 61508:2010, "Functional Safety of Electrical / Electronic / Programmable Electronic Safety-related Systems," 2010.

- [2] Core Knowledge on Instrumentation and Control Systems in Nuclear Power Plants, Technical Reports, IAEA Nuclear energy series no. NP-T-3.12, International Atomic Energy Agency, Vienna, 2011, 141 p. [Online]. Available: https://www-pub.iaea.org/MTCD/Publications/PDF/Pub1495 web.pdf

- [3] R.E. Hiromoto, A. Sachenko, V. Kochan, V. Koval, V. Turchenko, O. Roshchupkin, V. Yatskiv, K. Kovalok, "Mobile ad hoc wireless network for pre- and post-emergency situations in nuclear power plant," *Proceedings of the 2nd IEEE International Symposium on Wireless Systems within the Conferences on Intelligent Data Acquisition and Advanced Computing Systems*, Offenburg, Germany, 2014, pp. 92–96.

- [4] A.V. Palagin, and V.N. Opanasenko, "Design and application of the PLD-based reconfigurable devices," in book: *Design of Digital Systems and Devices, Lecture Notes in Electrical Engineering*, M. Adamski, A. Barkalov, M. Wegrzyn (Eds.), Springer, Verlag Berlin Heidelberg, vol. 79, pp. 59–91, 2011. DOI: https://doi.org/10.1007/978-3-642-17545-9 3.

- [5] R. Kochan, K. Lee, V. Kochan, A. Sachenko, "Development of a dynamically

- reprogrammable NCAP," Proceedings of the IMTC 2004 Instrumentation and Measurement Technology Conference, Como, Italy, 2004, pp. 1188–1193.

- [6] V.V. Sklyar, V.S. Kharchenko, "Fault-tolerant computer-aided control systems with multiversion threshold adaptation: Adaptation methods, reliability estimation, and choice of an architecture," *Automation and Remote Control*, vol. 63, no. 6, pp. 991–1003, 2002. DOI: https://doi.org/10.1023/A:1016130108770.

- [7] R. Seinauskas, R. Cvirka, G. Rudzioniene, "Acceleration of fault simulation based on a separate list of faults for each test pattern," *Elektronika ir Elektrotechnika*, vol. 21, no. 3, pp. 62–65, 2015. DOI: http://dx.doi.org/10.5755/j01.eee.21.3.5774

- [8] F. Sellers, M. Hsiao and L. Beamson, *Error Detecting Logic for Digital Computers*, New-York: Mc GRAW-HILL, 1968.

- [9] V. Hahanov, E. Litvinova, V. Obrizan, W. Gharibi, "Embedded method of SoC diagnosis," *Elektronika ir Elektrotechnika*, vol. 88, no. 8, pp. 3–8, 2008.

- [10] M. Nicolaidis, Y. Zorian, "On-line testing for VLSI a compendium of approaches," *Journal of Electronic Testing: Theory and Applications Special Issue on On-line testing*, vol. 12, pp. 7–20, 1998. DOI: 10.1023/A:1008244815697.

- [11] M. Abramovichi, C. Stroud, C. Hamiliton, S. Wijesuriya, V. Verma, "Using roving STARs for on-line testing and diagnosis of FPGAs in fault-tolerant applications," *Proceedings of the IEEE International Test Conference*, 1999, pp. 973–982. DOI: 10.1109/TEST.1999.805830.

- [12] ANSI/IEEE Std 754-1985, IEEE Standard for Binary Floating-Point Arithmetic, 1985.

- [13] IEEE Std 754<sup>TM</sup>-2008 (Revision of IEEE Std 754-1985) IEEE Standard for Floating-Point Arithmetic, USA, 2008.

- [14] H. Park, Truncated Multiplications and Divisions for the Negative Two's Complement Number System, Ph.D. Dissertation, The University of Texas at Austin, Austin, USA, 2007.

- [15] V. Garofalo, Truncated Binary Multipliers with Minimum Mean Square Error: Analytical Characterization, Circuit Implementation and Applications, Ph.D. Dissertation, University of Studies of Naples "Federico II", Naples, Italy, 2008.

- [16] V. Hema, M. Ganaga Durga, "Data integrity checking based on residue number system and chinese remainder theorem in cloud,"

- International Journal of Innovative Research in Science, Engineering and Technology, vol. 3, special issue 3, pp. 2584-2588, 2014.

- [17] A. Drozd, M. Lobachev, W. Hassonah, "Hardware check of arithmetic devices with abridged execution of operations," *Proceedings of the European Design and Test Conference*, Paris, France, 1996, pp. 611, 1996. DOI: 10.1109/EDTC.1996.494375.

- [18] D. Efanov, V. Sapozhnikov, Vl. Sapozhnikov, "Applications of modular summation codes to concurrent error detection systems for combinational Boolean circuits," *Automation and Remote Control*, vol. 76, issue 10, pp. 1834– 1848, 2015. DOI: 10.1134/S0005117915100112.

- [19] V.A. Romankevich, "Self-testing of multiprocessor systems with regular diagnostic connections," *Automation and Remote Control*, vol. 78, issue 2, pp. 289–299, 2017. DOI: 10.1134/S0005117917020084

- [20] M. Drozd, A. Drozd, "Safety-related instrumentation and control systems and a problem of the hidden faults," *Proceedings of the 10th International Conference on Digital Technologies 2014*, Zhilina, Slovak Republic, pp. 137–140, 2014. DOI: 10.1109/DT. 2014.6868692

- [21] D. Gillis, "The Apocalypses that Might Have Been," [Online]. Available: https://www. damninteresting.com/the-apocalypses-thatmight-have-been/

- [22] Department of Energy, DOE Guideline Root Cause Analysis Guidance Document, Office of Nuclear Energy and Office of Nuclear Safety Policy and Standards, Department of Energy, Washington DC, USA, 1992. http://tis.eh.doe.gov/techstds/standard/nst1004/nst1004.pdf

- [23] J. Jung, I. Ahmed, "Development of field programmable gate array-based reactor trip functions using systems engineering approach," *Nuclear Engineering and Technology*, March 2016, pp. 2–11. DOI: 10.1016/j.net.2016.02.011.

- [24] C. Metra, M. Favalli, B. Ricco, "Concurrent checking of clock signal correctness," *Proceedings of the IEEE Design & Test*, vol. 15, issue 4, pp. 42–48, 1998. DOI: 10.1109/54.735926.

- [25] Intel Quartus Prime Standard Edition User Guide: Getting Started, [Online]. Available: https://www.intel.com/content/www/us/en/prog rammable/documentation/yoq1529444104707. html

- [26] Intel Quartus Prime Standard Edition User Guide: Power Analysis and Optimization, [Online]. Available: https://www.intel.com/content/www/us/en/programmable/documentati on/xhv1529966780595.html

- [27] Xilinx ISE Design Suite, [Online]. Available: https://www.xilinx.com/products/design-tools/ise-design-suite.html

- [28] List of FPGA Companies, [Online]. Available: http://hardwarebee.com/list-fpga-companies/

- [29] MAX 10 FPGA Device Architecture, [Online]. Available: https://www.intel.com/content/www/us/en/programmable/documentation/sss1397439908414.html

- [30] Intel FPGA Integer Arithmetic IP Cores User Guide, [Online]. Available: https://www.intel.com/content/www/us/en/programmable/documentation/sam1395330298052.html

Oleksandr Drozd, Dr. Sci Eng., Professor of the Department of Computer Intelligent Systems and Networks of Odessa National Polytechnic University. Area of scientific interests: online testing and checkability of the digital components, safetycritical systems, FPGA-based systems.

Viktor Antoniuk, Master, Senior Lecturer of the Computer Department of Intelligent Systems and Networks of Odessa National Polytechnic University. Area of scientific interests: on-line testing and checkability of the digital components, FPGAbased systems.

Miroslav Drozd, Ph.D., Senior Lecturer of the Department of Information Systems of Odessa National Polytechnic University. of scientific Area interests: problem hidden fault and checkability of the digital components, FPGA-based systems.

Volodymyr Karpinskyy, Ph.D. Advanced Manufacturing Engi-(HSMW measurement neer lead) at the Complex Fabrications (Rolls-Royce plc.), Ph.D. in Mathematical modelling and computational methods, Ivan Puluj National Technical University, Ternopil, Ph.D. in Computer Science, West Pome-

ranian University of Technology, Szczecin, Poland. Research interests: mathematical modelling, metrology, computational methods, Computer Systems and Networks, Computer Science.

Pavlo Bykovyy, Bachelor (2004), Computer Engineering, Ternopil Academy of National Economy, Specialist (2005), Computer Systems and Networks, IEEE Member (2004), IEEE Student Branch Chairman in Ternopil State Economical University (2005), Ph. D. in Computer Systems

and Components (2011). Research interests: security systems, databases, software development.